Amazing Info About Why Verilog Is Better Than VHDL

Verilog vs. VHDL

1. A Quick Look at Hardware Description Languages

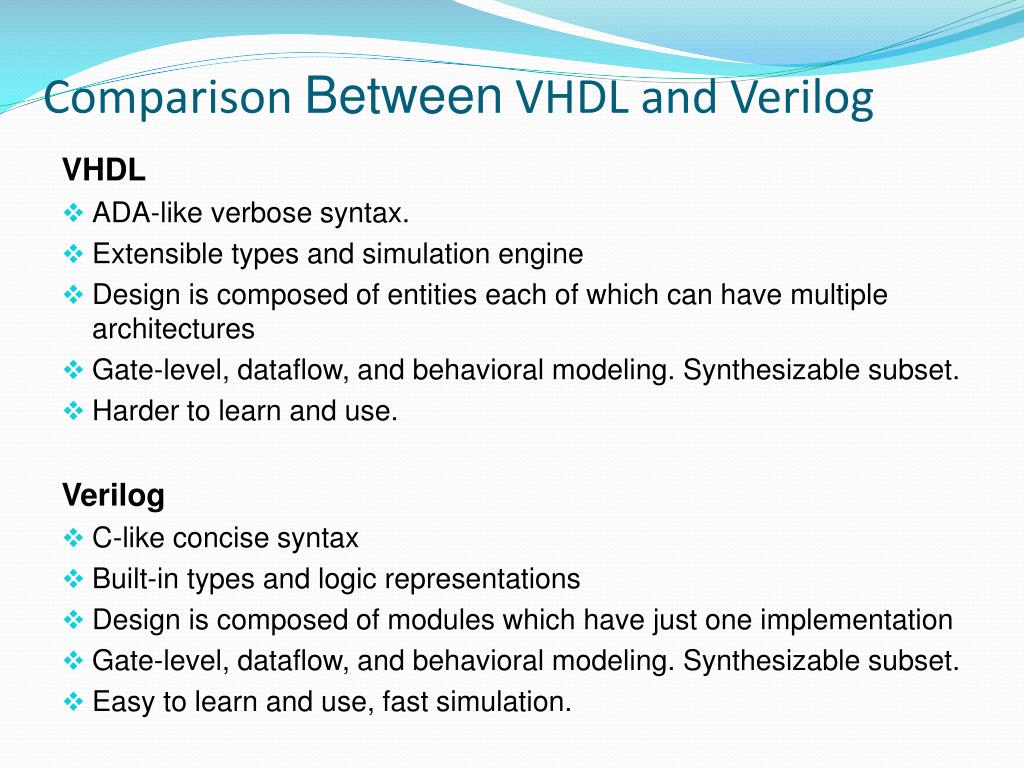

Okay, let's dive into the world of hardware description languages, or HDLs, for those not already swimming in the acronym soup. You've probably heard of Verilog and VHDL; they're like the Coke and Pepsi of digital circuit design. Both let you describe how electronic circuits should behave, but the burning question is: which one reigns supreme? Well, spoiler alert, this article is tilting towards Verilog — but we'll try to be fair!

Think of HDLs as blueprints for digital logic. Instead of drawing schematics with gates and wires, you write code that describes the circuit's function. This makes designing complex systems much easier to manage. Need to change something? Just tweak the code and re-synthesize it, rather than rewiring a breadboard. Plus, HDLs allow for simulation, meaning you can test your designs before committing them to physical hardware. This saves time, money, and a whole lot of potential frustration.

Now, both Verilog and VHDL are perfectly capable of getting the job done. They can both describe combinational logic, sequential logic, state machines — the whole shebang. However, there are some key differences in syntax, features, and overall philosophy that can make one a better choice than the other, depending on the project and the designer's preferences. Keep reading, and we'll explore why I believe Verilog often comes out on top.

Ultimately, understanding both Verilog and VHDL is a fantastic skill for any aspiring or seasoned hardware engineer. However, if you're just starting out, or you're deciding which to focus on, I believe Verilog offers a slightly smoother learning curve and better industry compatibility, especially in certain areas. So, let's delve deeper into the reasons why Verilog might just be your HDL soulmate!

Verilog Vs VHDL Learn The Key Differences Of And, 43 OFF

Why Verilog Often Takes the Crown

2. Simplicity and Learning Curve

One of the biggest advantages of Verilog is its relatively simple syntax. Coming from a C background? You'll feel right at home! Verilog borrows heavily from C, making it easier to pick up for programmers already familiar with that language. This means less time spent wrestling with syntax and more time spent designing cool stuff.

VHDL, on the other hand, can be a bit more verbose and require a deeper understanding of its underlying concepts. It's a very powerful language, no doubt, but the initial learning curve can be steeper. Think of Verilog as learning to ride a bike with training wheels, while VHDL is more like jumping straight onto a unicycle. Both will get you there eventually, but one is definitely less likely to result in faceplanting.

This ease of learning translates to faster development times, especially for smaller projects or when working with designers who are new to HDLs. The reduced complexity also means less time spent debugging syntax errors, which is always a good thing. We've all been there, staring at a screen, trying to figure out why the compiler is yelling at us. Verilog helps minimize those moments.

Consider the initial barrier to entry. If you need to get a team up to speed quickly on a new project, Verilog's more accessible syntax can be a real lifesaver. It allows engineers to focus on the design logic rather than getting bogged down in the intricacies of the language itself. This streamlined approach contributes to faster project completion and reduced development costs.

VHDL Vs Verilog SystemVerilog Which Hardware Language Should You

Industry Adoption and Tool Support

3. Verilog's Prevalence in the Semiconductor World

Another compelling reason to favor Verilog is its widespread adoption in the semiconductor industry, especially in North America and Asia. While VHDL has its strongholds, particularly in Europe and in government/military applications, Verilog often dominates in chip design and verification. This means more job opportunities for Verilog experts and a larger community to draw support from.

The prevalence of Verilog also translates to better tool support. Many EDA (Electronic Design Automation) vendors prioritize Verilog in their development and optimization efforts. This leads to more mature and feature-rich tools for Verilog design, simulation, and synthesis. Think of it as having a wider selection of high-quality paintbrushes when creating your masterpiece.

Furthermore, a larger user base means a more active online community, with plenty of forums, tutorials, and code examples to help you along the way. Stuck on a problem? Chances are, someone else has already encountered it and posted a solution online. This collaborative environment can be invaluable when you're facing a challenging design issue.

Of course, VHDL is still widely used, and it's important not to discount its significance. However, when it comes to sheer volume of projects and available resources, Verilog often holds a slight edge, particularly in the commercial sector. This makes Verilog a pragmatic choice for those seeking the greatest opportunities and the widest range of support.

Verilog Vs VHDL Differences & FPGA Digilent Blog

Handling Complex Designs

4. Where Verilog Shines

While both languages are capable, Verilog's often considered more straightforward for handling complex digital designs. This stems from its less rigid structure and more direct approach to describing hardware behavior. Designers can often express their ideas more concisely and intuitively in Verilog, leading to more readable and maintainable code.

Verilog offers powerful constructs for modeling hardware behavior at different levels of abstraction, from gate-level descriptions to behavioral models. This flexibility allows designers to choose the most appropriate level of detail for each part of their design, optimizing for performance and simulation speed. Need to model a complex component without getting bogged down in the details? Verilog makes it easier to do so.

Moreover, Verilog's syntax is generally more forgiving than VHDL's, allowing for a more iterative design process. Designers can quickly prototype and test different design ideas without having to worry about strict adherence to coding standards. This encourages experimentation and innovation, leading to more efficient and creative solutions.

Consider the example of designing a complex state machine. While VHDL can certainly handle this task, Verilog's more intuitive syntax and powerful features for behavioral modeling often make it a more natural choice for expressing the desired functionality. This ease of use can translate to faster design cycles and a more streamlined development process.

![Unerring Language VHDL Vs VERILOG [2023] Unerring Language VHDL Vs VERILOG [2023]](https://www.logic-fruit.com/wp-content/uploads/2021/09/VHDL-VS-VERILOG-Thumbnail-1024x538.jpg)

Beyond the Basics

5. Verilog's Role in the Modern Design Flow

Verilog isn't just about describing hardware; it's also a crucial part of the verification process. SystemVerilog, an extension of Verilog, is widely used for functional verification, incorporating features like constrained-random stimulus generation and coverage-driven verification. This allows engineers to thoroughly test their designs and ensure they meet specifications before committing them to hardware.

The adoption of SystemVerilog for verification has further solidified Verilog's position as a dominant HDL in the industry. It provides a comprehensive toolset for creating robust and reliable digital designs. While VHDL also has its verification capabilities, SystemVerilog is often preferred for its wider adoption and more mature tool support.

Moreover, Verilog is often used in conjunction with other languages and tools in the design flow. For example, it can be used to describe the hardware architecture of a system-on-chip (SoC), while C or C++ is used to develop the embedded software. This seamless integration allows for co-simulation and co-verification, ensuring that the hardware and software components work together seamlessly.

So, when you're considering which HDL to learn, remember that it's not just about the language itself, but also about the ecosystem of tools, resources, and expertise that surrounds it. Verilog, with its strong industry adoption, comprehensive verification capabilities, and seamless integration with other tools, often provides a more advantageous starting point for aspiring hardware engineers.